摘 要:为了研究 H D B3 码的编码原理,采用了两种方法来实现 H D B3 码编码器。方案一:先进行非 0 码的极性变化及带极性的插 V 操作,然后再进行带极性插 B 操作;方案二:先进行插 V 操作,再进行插 B 操作,最后再进行极性变化。最后验证可得,当时钟频率为 100 M H z时,虽然两种方案都能实现 H D B3 码的编码,并且功耗相同,但是两种方案硬件电路所占用的总逻辑单元不相同,方案二占用的总逻辑单元比方案一少 9 个。因此,在功耗一定的情况下,方案二优于方案一。

关键词:FPG A ;H D B3 码;逻辑资源;功耗

为了适应信道,信号在传输前一般要进行编码处理[1]。编码形式多种多样,而 H D B3 码低频成分少,连续的 0 不超过 3 个,而且无直流特性,所以应用范围较广[2]。本研究采用 V H D L 语言,设计了两种 H D B3 码编码器,并对这两种编码系统进行了对比分析[3]。

1、码编码原理

H D B3 码主要由 3 个关键步骤获得:序列极性变化、序列插 V 操作及序列插 B 操作[4]。

序列极性变化:检测到非 0 码时,将其极性依次正负变化[5 6]。

序列插 V 操作:序列中若检测到连续 4 个 0,则在该处插入 V ,其他情况原样输出。

序列插 B 操作:判断输入序列中两个相邻 V 符号之间的非 0 码个数,如果其值为偶数,那么便将 B 码插入序列中对应的位置,否则就保持原样输出。

本设计中,两种方案的 3 个关键步骤执行顺序不一样。方案一首先对序列进行非 0 码极性变化及带极性插 V 操作,然后再对序列进行带极性插 B 操作;方案二首先进行插 V 操作,然后再进行插 B 操作,最后再进行极性变化。

2、码的硬件电路

2.1 方案一的硬件电路

chaV 是非 0 码极性形成及带极性插 V 模块,在此硬件电路中,该功能模块用 flag_v_1﹙flag_v_v﹚代表前 一个非 0 码﹙前一 V 码﹚的极性,若标志信号为 0 则代表极性为负,若为 1 则为正[7]。当输入信号 input为 1 时,根据 flag_v_1 的值,out_v 输出对应的极性信号[8];当输入信号 input为 0 时,那么内置计数器就进行加一操作,与此同时判断该计数器的值是否等于 4,如果刚好等于 4,那么 out_v 端口便输出一个 V﹙首个 V 的正负号与前一个非 0 符号保持相同,后面 V 的符号正负变化﹚,否则原样输出[9]。

chaB 是带极性的插 B 模块,在此硬件电路中,该功能模块采用四位移位寄存器来进行带极性插 B 操作,当 chaV 模块的输出信号 out_v 输入移位寄存器时,chaB 模块中的移位寄存器的第四级同时判断该输入信号是否为 V﹙+ V 或 V﹚,如果是,便继续判断当前 V 的极性是否和前一个非 0 码极性相同。如果相同,那么 out_b 便原样输出,如果不相同,那么 out_b 便输出与当前 V 极性相同的 B﹙由于采用了移位寄存器,使得最后输出的 B 在两个 V 码之间后一个非 0 符号后﹚。

2.2 方案二的硬件电路

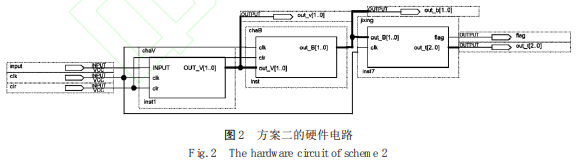

方案二的硬件电路如图 2 所示,chaV 、chaB、jixing 分别是插 V 模块、插 B 模块和极性形成模块。

在此硬件电路中,chaV 模块先判断输入信号 input是否为 0,若是,则继续判断是否为第 4 个 0,若是,则将 out_v 输出 V﹙不带极性﹚,其他情况原样输出。chaB 模块采用四位移位寄存器来进行不带极性插 B 操作,当 chaV 模块输出的信号 out_v 输入移位寄存器时,chaB 模块中的移位寄存器的第 4 级同时判断该输入信号是否为 V 。若是 V ,则开始计数非 0 码的个数,直到下一个 V 结束计数,同时判断该计数值的奇偶性,若为偶数,则输出 B﹙由于 chaB 模块采用了移位寄存器,使得最终输出的 B 在 2 个 V 码中后一非 0 符号后﹚,否则原样输出。

当 out_b 信号进入 jixing 模块时,该模块根据 flag 信号﹙前一非 0 码与 B 的极性标志﹚对 0 和 B 进行正负极性交替,同时也可得到 V 的极性,故输出 H D B3 码 out_t。

3、仿真结果及分析

3.1 方案一的仿真结果与分析

在此方案中,input是输入的待编码信号,clk 为 100 M H z时钟端,clr是清零端,flag_v_1、flag_v_v 分别是前一非 0 码、前一 V 码的极性标志。由仿真可得,当输入 10011000011100001100001011 时,插 V 操作及极性形成信号 out_v 是 + 100 1 + 1000 + V 1 + 1 1000 V + 1 1000 + V 10 + 1 1﹙如果用 0 代表 0,1 代表 B,2 代 表 1,3 代 表 V ,5 代 表 + B,6 代 表 + 1,7 代 表 + V ,那 么 对 应 的 十 进 制 为 60026000726200036200072062﹚,插 B 后的信号﹙H D B3 码编码信号﹚out_b 是 + 100 1 + 1000 + V 1 + 11000 V + 1 1 + B00 + V 1 + 1 1﹙对应的十进制为 60026000726200036250072062﹚。但由于使用了移位寄存器,导致输出有延迟[10]。

方案一的功耗如图 4 所示,总功耗为 63.86 m W ,静态功耗为 60.15 m W ,I/O 功耗为 3.71 m W 。

方案一的资源占用如图 5 所示,组合逻辑占用 57 个,逻辑单元共占用 69 个。

3.2 方案二的仿真结果与分析

方案二的仿真结果如图 6 所示

10011000V 111000V 11000V 1011﹙其中 0 代 表 0,1 代 表 1,2 代 表 B,3 代 表 V ,那 么 对 应 的 十 进 制 为 10011000311100031100031011﹚,插 B 操作后的信号 out_b 是 0011000V 111000V 11B00V 1011﹙0 代表 0,1 代表 1,2 代表 B,3 代表 V ,那么对应的十进制为 10011000311100031120031011 ﹚。极性转化后的信号﹙H D B3 码编码信号﹚out_t是 + 100 1 + 1000 + V 1 + 1 1000 V + 1 1 + B00 + V 10 + 1 1﹙0 代表 0,1 代表 B,2 代 表 1,3 代 表 V ,5 代 表 + B,6 代 表 + 1,7 代 表 + V ,那 么 对 应 的 十 进 制 为 60026000726200036250072062﹚。但由于使用了移位寄存器,导致输出有延迟。

方案二的功耗如图 7 所示,总功耗为 63.86 m W ,静态功耗为 60.15 m W ,I/O 功耗为 3.71 m W 。

4、对比分析

本设计中,两种方案的 3 个关键步骤执行顺序不一样,方案一首先进行非 0 码极性变化及带极性插 V 操作、然后再进行带极性插 B 操作;方案二首先进行插 V 操作,然后进行插 B 操作,最后再进行极性变化。虽然上述两种方案都能对输入信号进行 H D B3 码编码,并且功耗相同,但所占用的逻辑资源不同,性能比较如表 1 所示。

从表 1 可以看出,在功耗相同的情况下,方案二占用的总逻辑单元比方案一少 9 个,所以相对来说方案二优于方案一。本程序设计可能不是最优的,结果还稍有误差,所以在后续的工作中需要继续优化这两种方案。——论文作者:杨 盢,肖顺文

参考文献:

[1] 段吉海,黄智伟.数字通信系统建模与设计[M ].北京:电子工业出版社,2004:1 288.

[2] 樊昌信,张甫翊,吴成柯.通信原理[M ].5 版.北京:国防工业出版社,2001:77 78.

[3] 徐斌.基于 FPG A 的 LD PC 码译码器研究[D ].厦门:华侨大学,2018.

[4] 龙光利.基于 CPLD 的 H D B3 码编解码电路的设计[J].微计算机信息,2010,26﹙2﹚:169 171.

[5] 谢文涛.基于 SO PC 技术的 H D B3 编码器设计[D ].西安:长安大学,2014.

[6] 李春晖.基于 System V iew 的 H D B3 编码器设计[J].信息通信,2014﹙9﹚:41.

[7] 郝志强,刘兴斌,胡金海,等.基于 FPG A 的 H D B3 编解码方法及其在阵列电导探针流动测井中的应用[J].石油仪器, 2012,26﹙2﹚:76 79.

[8] 程斌.三阶高密度双极性 H D B3 码编解码的 V H D L 设计及仿真[D ].苏州:苏州大学,2008.

[9] 王晓聪,何永泰.基于 FPG A 的 H D B3 码编码器优化设计与分析[J].现代电子技术,2011,34﹙24﹚:146 148.

[10] 潘松,黄继业.ED A 实用教程[M ].北京:科学出版社,2005:77 79.

* 稍后学术顾问联系您